# Design and Implementation of 4x4 bit Multiplier using Dadda Algorithm

Dr.K.Ragini Professor, B.Neerajakshi M.Tech Student

G.Narayanamma Institute of Technology and Science, Shaikpet, Hyderabad, India,

G.Narayanamma Institute of Technology and Science, Shaikpet, Hyderabad, India.

# ABSTRACT

Multiplier is one of the most important arithmetic modules in the fast computing applications. Multipliers and their associated circuits like half adders, full adders and accumulators consume a significant portion of most high speed applications. In order to reduce the hardware which ultimately reduces an area, power and propagation delay, efficient full adders are used in the multipliers. They also reduce the power and propagation delay of the multiplier. In this paper 4x4 multiplier is designed using Dadda algorithm and 10T full adder. Use of Dadda algorithm reduces 10.47% of the power dissipation, 27.67% of the propagation delay and 35.34% power delay product compared to Array multiplier. The simulations are performed using Tanner EDA of 45nm technology.

## **Keywords:**

Multiplier, Full adder, Half Adder, Array, Wallace, Vedic, Dadda, Power dissipation, Propagation Delay, Power delay product.

## **1.INTRODUCTION**

Multiplier plays an important role in digital signal processors and various other applications. More than 70% of instructions in microprocessors are performing addition and multiplication operations, so these operations are dominating the execution time of processor. There is a need of high speed multiplier to decrease the execution time of the processor and also in the VLSI design power dissipation, propagation delay and area are the important parameters which should be taken into consideration. In the design of multiplier more number of full adder blocks is used. Decrease of power consumption and propagation delay in the full adder can decrease the total power consumption and propagation delay of the multiplier. So here low power and high speed multiplier is implemented using Dadda algorithm and 10T full adder. Section-2 describes the Existing multipliers like Array, Wallace and Vedic multiplier. Section-3 describes the proposed multiplier which is Dadda multiplier. Section-4 contains the results and discussions. Section-5 concludes the paper.

## 2. Existing Multipliers:

## 2.1 Array Multiplier:

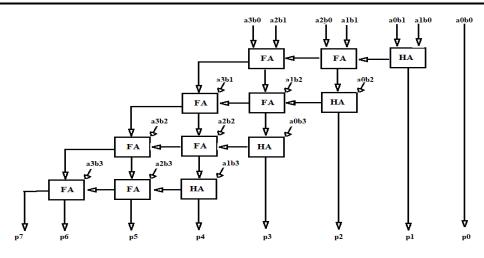

It is the conventional Multiplier. It uses the same steps as used in the normal multiplication. It is based on shift and add algorithm. 4x4 multiplier uses 16 AND gates, 4 half adders, 8 full adders and 12 total adders are used [2]. In Fig.1 a0, a1, a2 and a3 are bits in the multiplicand and b0, b1, b2 and b3 are the bits in multiplier. P0, p1, p2, p3, p4, p5, p6 and p7 are the output bits. Where HA is the half adder and FA is the full adder.

Fig.1 4x4 Array Multiplier

It has a regular structure. It is easy for implementation, but it consumes more power. Use of large number of digital gates resulted in large chip area. For further reduction of power dissipation and propagation delay, different multipliers are designed based on the different algorithms.

#### 2.2 Wallace Multiplier

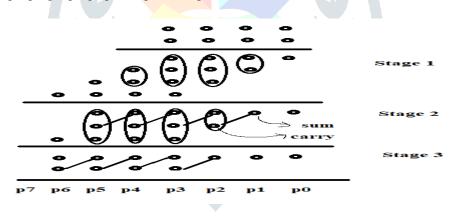

Every Multiplication algorithm consists of three stages. They are i) Generation of partial products ii) Reduction of partial products iii) Addition of partial products. Generation of partial products is same in every algorithm. In the reduction process, use full adders wherever the three elements are present. And use half adders wherever the two elements are there. Generated sum and carry bits from the half and full adders will be passed to the next stage. Pass the left over elements to the next stage. Repeat this process until getting the two rows [1][6]. Figure.3 shows the dot diagram of Wallace multiplier. Finally add last two rows to get the output [3]. In Fig.2 p0, p1, p2, p3, p4, p5,p6 and p7 are output bits.

Fig.2 4x4 Wallace algorithm dot diagram [1]

## 2.3 Vedic Multiplier:

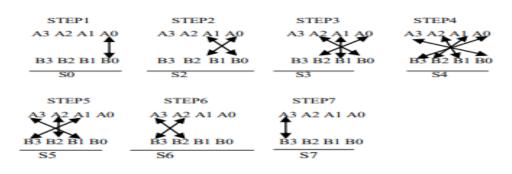

It is based on the vertically and crosswise method. Consider two numbers A=A3A2A1A0 and B=B3B2B1B0. A3, A2, A1, A0, B3, B2, B1 and B0 are the bits in the number. Multiply A0 and B0 and the result is sum s0. In the step2, multiply A0 and B1 and add the result to the product of A1 and B0. The result obtained is s1 and the carry is c1. In this manner multiply and add the bits as shown in Fig.3 for remaining steps. Here carry generated from one step will be added to the sum in the next step [7].

Figure.3 4x4 Vedic Multiplier

| Step | 1:S0= | A0B0 |

|------|-------|------|

| ~~~~ |       | 1020 |

| <b>Step2:</b> S1=A1B0+A0B1;              |                   | sum=S1, carry=C1; |

|------------------------------------------|-------------------|-------------------|

| <b>Step3:</b> S2=A2B0+A1B1+A0B2+C1;      | sum=S2, carry=C2; |                   |

| <b>Step4:</b> S3=A3B0+A0B3+A2B1+A1B2+C2; |                   | sum=S3, carry=C3; |

| <b>Step5:</b> S4=A3B1+A1B3+A2B2+C3;      |                   | sum=S4, carry=C4; |

| <b>Step6:</b> S5=A3B2+A2B3+C4;           | JL                | sum=S5, carry=C5; |

| <b>Step7:</b> S6=A3B3+C5;                |                   | sum=S6, carry=C6; |

| Final Output=C6S6S5S4S3S2S1S0.           |                   |                   |

Here in this multiplier 4 full adders and three half adders are used. It is more efficient than Array and Wallace multipliers in terms of power and propagation delay. The disadvantage of this multiplier is that the system becomes complex for complex numbers.

### 3. Proposed Multiplier

### 3.1 Dadda Multiplier:

Array multiplier has more power consumption and propagation delay compared to other multipliers. Wallace multiplier has large area wastage problem due to irregularity in the structure. Vedic multiplier system becomes complex for complex numbers. To overcome these disadvantages in the existing multipliers Dadda multiplier is proposed.

Dadda multiplier is a fast parallel multiplier presented by Luigi Dadda in 1965. It is a refinement of Wallace multiplier so its algorithm also has three general stages. The procedure of the three stages is same for Dadda multiplier as in Wallace multiplier. But in Dadda multiplier, the row reduction processed by placing adders at maximum heights of matrix in optimal manner. Thus it requires less adders compared to Wallace multiplier.

Reduction process is controlled by dj value. Where dj is the maximum height of the sequence, dj=2 then dj+1=floor(15dj) The sequence is  $d_1=2$ ,  $d_2=3$ ,  $d_3=4$ ,  $d_4=6$ ,  $d_5=9$ ,  $d_6=13$ ....The initial value of  $d_j$  is chosen as the largest value such that  $d_j < \min(m, n)$ . Where m and n are the input bits in the input multiplicand and multiplier. If height  $(C_i) \le d_j$  then that column does not require reduction, move to next column. If height of of  $C_i=d_{j+1}$  add top two elements in a half adder, place the result at the bottom of the column and carry at the top of column  $C_{i+1}$ , then move to column  $C_{i+1}$ . Else add top three elements in a full adder, place the result at the bottom of the column and carry at the bottom of the column and carry at the top of the column  $C_{i+1}$ , restart  $C_i$  at step1.

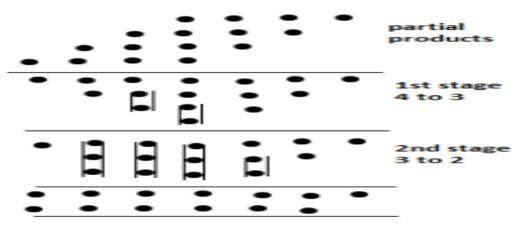

Fig.4 4x4 Dadda algorithm dot diagram

4x4 bit Dadda multiplier algorithm process is shown in Fig.4. The number of full and half adders needed for Dadda multiplier is depend on size of the operands, determined by the following equations [5].

Number of Full adders required = 3

Number of half adders required = 3

Thus the Dadda multiplier requires less number of adders compared to all other multipliers. Hence area of multiplier is reduced .The power dissipation is reduced and speed is also reduced, because of reduction of partial products which is necessary at each level.

# 4. Simulation Results of Existing and Proposed Multipliers

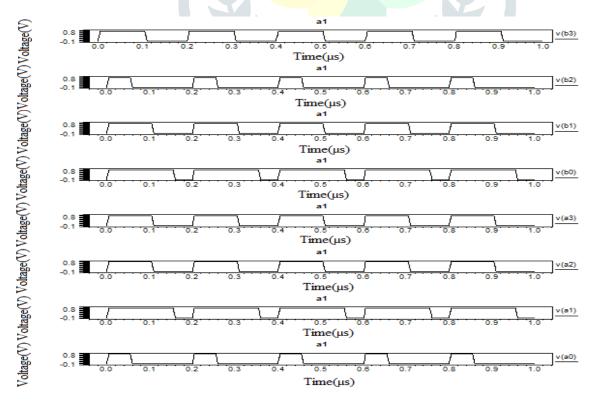

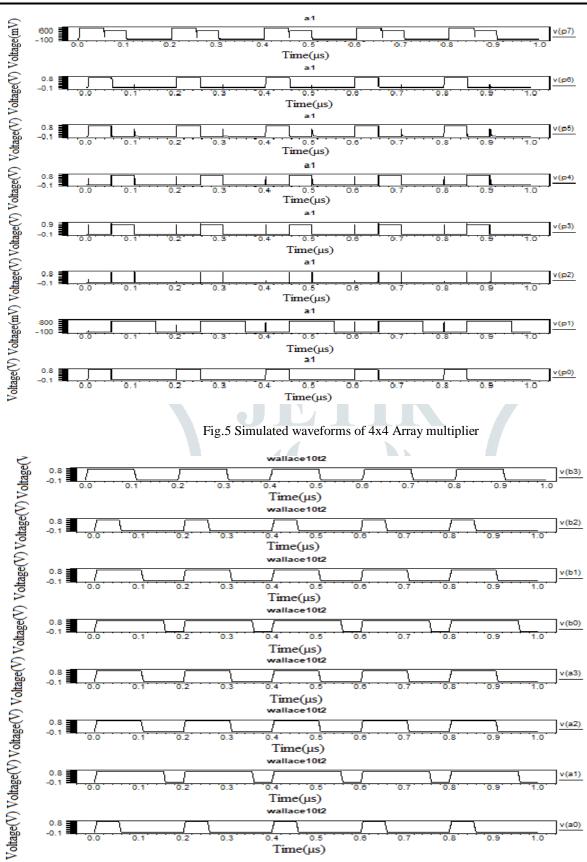

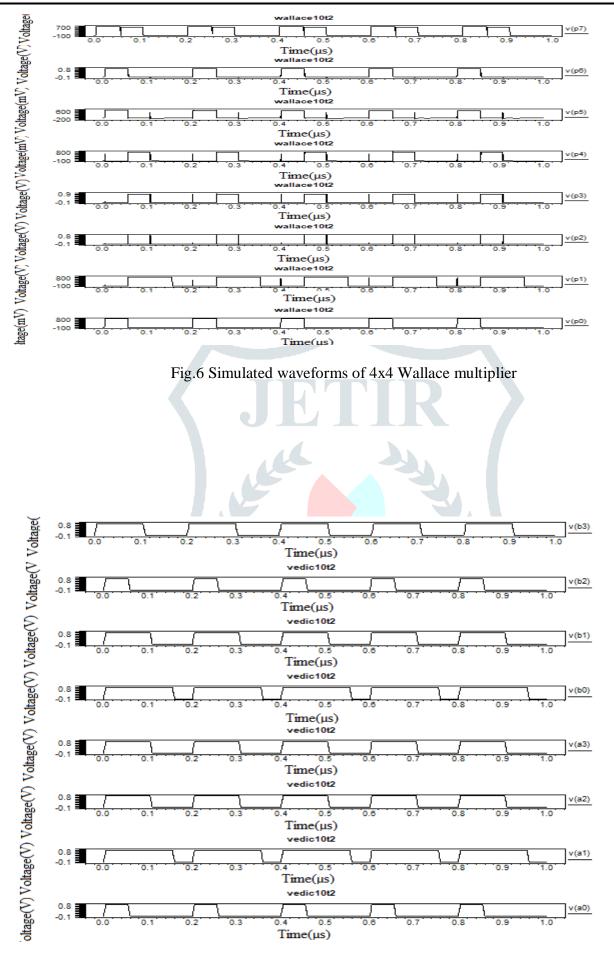

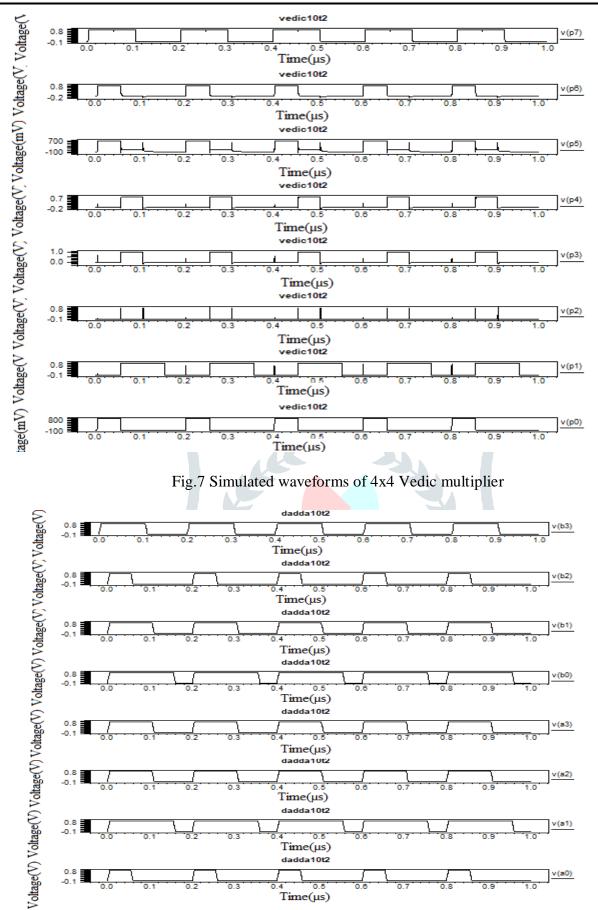

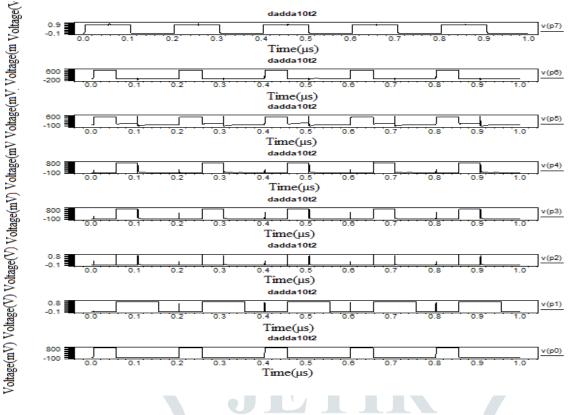

Simulations are performed using Tanner EDA tool. The inputs to the multiplier are A=a3a2a1a0 and B=b3b2b1b0. The simulation waveforms analyzed for different multiplier circuits with the inputs a0=1000, a1=1110, a2=1100, a3=1100 and b0=1110, b1=1100, b2=1000 and b3=1100. The results are shown in figures.

+

Fig.9 Simulated waveforms of 4x4 Dadda multiplier

From the results, all the multipliers are functioning properly at 45nm technology with  $V_{dd}=1V$ . The power, propagation delay and power delay product are observed for different 4x4 multipliers and the results are tabulated.

Simulation results of existing and proposed multipliers:

| 4x4 multiplier | Power(µw) | Propag <mark>ation Delay</mark> (µs) | Power delay product(pJ) |

|----------------|-----------|--------------------------------------|-------------------------|

| Array          | 39.4      | 2.1                                  | 0.843                   |

| Wallace        | 37.7      | 1.8                                  | 0.692                   |

| Vedic          | 35.3      | 1.7                                  | 0.615                   |

| Dadda          | 35.3      | 1.6                                  | 0.545                   |

#### **Result Analysis:**

Array multiplier has more power consumption and propagation delay compared to all other 4x4 multipliers like Wallace, Vedic and Dadda multipliers. Because more number of full adders is used in the Array multiplier compared to other multipliers. Carry generated from one adder is the input to the other adder. In the generation of output bit of p7, it has to travel from the first half adder in the first stage to final stage. So the propagation delay is more in this multiplier. Here more number of digital gates is used so the power consumption and chip area are more. Every adder has partial product inputs, sum and carry inputs and two outputs. So it has regular structure.

Wallace multiplier has simple carry propagate adder compared to other multipliers but Wallace multiplier is less regular than Array multiplier. Because of the less regularity it is suffering from the large area wastage.

Vedic multiplier performs the fast multiplication. But as the number of bits increases, system becomes complex. Carry propagate adder used in the Vedic multiplier is high compared to Wallace multiplier and power consumption and propagation delay are less compared to Array and Wallace multipliers.

Multipliers vary depending on the partial product reduction algorithms used in the multiplier designs. The purpose of algorithms used in the digital design is the reduction of hardware. Dadda multiplier uses 3 full adders, Vedic multiplier uses 4 full

adders and Wallace multiplier uses 3 full adders, so number of full adders used in the Dadda multiplier is less compared to other multipliers and number of half adders used in the Dadda multiplier also less so the power consumption of Dadda multiplier is less.

#### 5. Conclusions and Future Scope

Proposed Dadda multiplier has low power consumption and low propagation delay compared to existing multipliers where as Array multiplier has more power consumption, propagation delay and power delay product. Dadda multiplier has achieved 10.47% reduction in power dissipation, 27.67% reduction in propagation delay and 35.34% power delay product compared to Array multiplier.

These multiplier designs can be implemented for 8x8 multipliers. Every multiplier has its own advantages and disadvantages using hybrid techniques new multiplier design can be implemented. Dadda multiplier has the complex carry propagate adder at the final stage whereas the Wallace multiplier has less complex carry propagate adder. By combining these two algorithms new hybrid multiplier can be designed.

#### REFERENCES

[1] G.Challa Ram, D.Sudha Rani, R.Balasaikesava, K.Bala Sindhuri "Design of Delay Efficient Modified 16 bit Wallace Multiplier" IEEE International Conference On Recent Trends In Electronics Information Communication Technology, India, May 20-21, 2016.

[2] S.Srikanth, ThahiraBanu, G.VishnuPriya, G.Usha "Low Power Array Multiplier Using Modified Full Adder" 2nd IEEE International Conference on Engineering and Technology (ICETECH), Coimbatore, TN, India, 17th & 18th March 2016.

[3] R.Naveen, K.Thanushkodi, Preeti, C Saranya, "A survey of low power Wallace and Dadda Multipliers using different logic full adders". International Journal of Research in Engineering and Technology, vol.3, Issue 11, pISSN: 2321-7308, 2014.

[4] Sumod Abraham, Sukhmeet Kaur, Shivani Singh, "Study of Various High Speed Multipliers" 2015 International Conference on Computer Communication and Informatics (ICCCI -2015), Jan. 08 – 10, Coimbatore, INDIA, 2015.

[5] Muhammad Hussnain Riaz, Syed Adrees Ahmed, Qasim Javaid, Tariq Kamal," Low Power 4×4 Bit Multiplier Design using Dadda Algorithm and Optimized Full Adder" 15<sup>th</sup> international Bhurban Conference on applied science & Technology(IBCAST) Islamabad, Pakistan, 9<sup>th</sup>-13<sup>th</sup> january, 2018.

[6] G.Challa Ram, D.Sudha Rani, R.Balasaikesava, K.Bala Sindhuri "Design of Delay Efficient Modified 16 bit Wallace Multiplier" IEEE International Conference On Recent Trends In Electronics Information Communication Technology, India, May 20-21, 2016.

[7] Abhyarthana Bisoyil, Mitu Baratl, Manoja Kumar Senapati "Comparison of a 32-Bit Vedic Multiplier With A Conventional Binary Multiplier" IEEE International Conference on Advanced Communication Control and Computing Technologies (ICACCCT), 2014.

[8] R. Zimmermann, W. Fichtner, "Low power logic styles: CMOS versus pass transistor logic", IEEE J. Solid State Circuits 32, 1079–1090 (1997).

[9] Jeevan, B., Narender S., Dr. C.V. Krishna Reddy and Dr. K. Sivani ,"A high speed binary floating point multiplier using Dadda algorithm.", International Multi-Conference IEEE on Automation, Computing, Communication, Control and Compressed Sensing, 2013.

[10] Wallace, C.S., "A Suggestion for a Fast Multiplier", IEEE Trans. Electron. Compt., vol. 13, no. 1, pp. 14-17, Feb., 1964.

[11] Ron S. Waters and Earl E. Swartzlander, Jr., "A Reduced Complexity Wallace Multiplier Reduction", IEEE Trans., pp. 1134-1137, Aug., 2010.

[12] K.C.Bickerstaff and E.E. Swartzlander, Jr. "Analysis of Column Compression Multipliers," in 15th IEEE Symposium on Computer Arithmetic, 2001.

[13]S. S. Kidambi, F. El-Guibaly, and A. Antoniou, "Area- efficient multipliers for digital signal processing applications," IEEE Trans. Circuits Syst. II, Exp. Briefs, vol. 43, no. 2, pp. 90–95, Feb. 1996.

[14] I.S.Ab u-Khater, A.Bellaouar , and M.I.Elmasry , Circuit techniques for CMOS low power high-performance multipliers. IEEE Journal of Solid State Circuits, Vol.31, pp.1535–1546. 1996.

[15] Wey C.L, Chang T.Y, "Design and Analysis of VLSI based parallel multipliers", IEEE Proceedings on Computer and Digital Techniques, Vol 137, pp 328-336, July 1999.

[16] Parth Mehta, Dhanashri Gawali, "Conventional versus Vedic mathematical method for Hardware implementation of a multiplier", IEEE Int. Conf. on Advances in Computing, Control, and Telecommun. Technologies, pp. 640-642, 2009.

[17] G.Ganesh Kumar and V.Charishma, "Design of High Speed Vedic Multiplier using Vedic Mathematics Techniques", Int. Journ. of Scientific and Research Publication, vol. 2, March 2012.